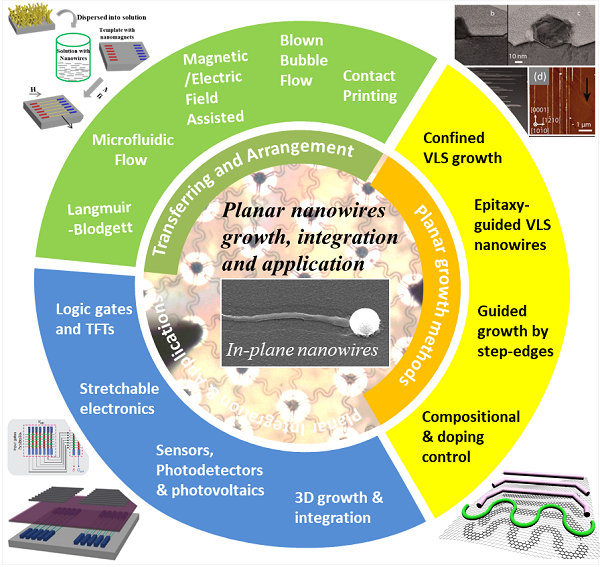

准一维(Quasi one-dimensional, 1D)半导体纳米线(Semiconductor Nanowires)是开发新一代高性能电子器件最理想、最方便的构建单元,也是构建超高效光电探测调控和新颖微纳机电器件的关键基础。相比于传统“自上而下”的刻蚀制备工艺,自组装生长半导体纳米线结构在尺寸调控、制备成本和三维形貌等方面有着显著的优势,近年来在高性能逻辑、生物传感和柔性显示等新兴应用领域中广受关注。然而,如何在主流平面工艺框架中,实现自组装半导体纳米线的精准定位和规模集成,一直是巨大的技术挑战--被当今学术界广泛认为是突破和推广纳米线技术应用的“最后一个技术障碍”。聚焦于平面纳米线生长、集成和器件应用的研究进展,南京大学余林蔚、徐骏教授课题组应邀在《先进材料》上撰写长文综述,系统介绍近二十年来自组装半导体纳米线研究的发展历程,关键技术突破和目前所面临的主要困难。通过对文献的深入跟踪分析,发现近期研究关注热点正逐步转移和聚焦于更为贴近产业化应用需求的“平面纳米线生长调控和规模集成技术”。这个转变的发生出现在半导体纳米线研究日益成熟的大背景下,一方面体现了产业升级对采用高性能纳米线结构/技术的迫切需求,另一方面也反应了学术界对规模化可控制备和集成的高度关注和重视。

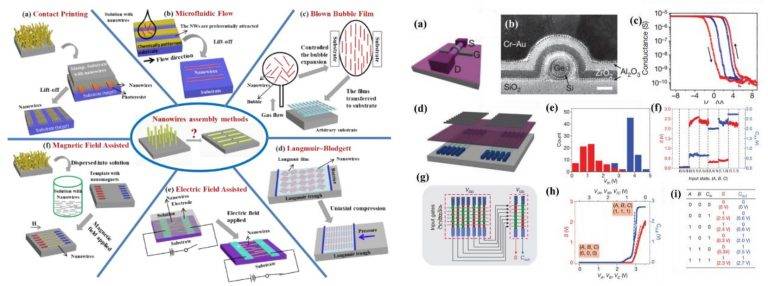

文章首先回顾了基于早期竖直生长纳米线实现的平面集成工艺:由于采用气态前驱体供给模式(例如vapor-liquid-solid,VLS生长机理),还需要将竖直纳米线收集、转移和在平面衬底上进行排布,以便于后续的电极连接和器件集成。为此,可以采用Contact Printing, Microfluidic flow, Bubble film, Langmuir-Blodgett, Electric/Magnetic field assisted等一系列不同的技术方案。虽然以上方法在定向转移和平面排布方面展示了一定的成功,但在与现有平面工艺兼容、降低制备成本和突破纳米线精确定位等关键问题上依然还面临着很大的技术困难和挑战。

图1:(左)基于“先生长-再转移”策略的各种平面纳米线定向规则排布技术;(右)利用VLS生长并转移组装的Ge/Si核壳结构纳米线阵列逻辑原型器件。

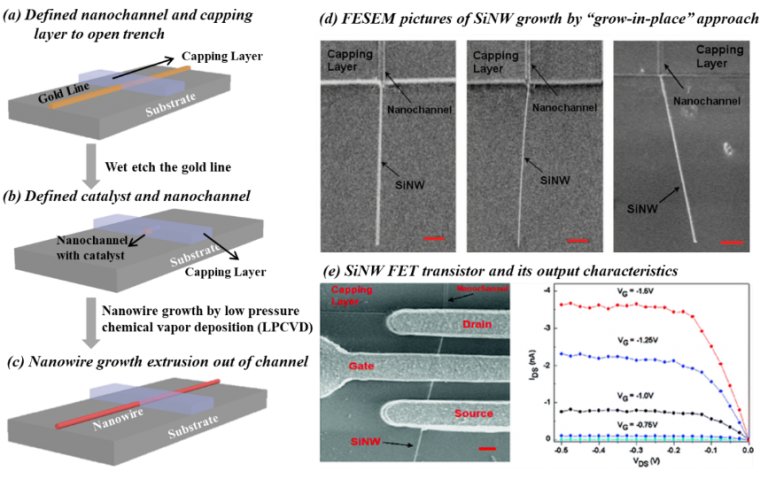

因此,文章重点介绍了更为直接有效的平面纳米线生长技术。1)首先,基于传统VLS生长模式和预设表面沟槽实现的限制纳米线平面引导生长:利用高精度光刻预先在衬底表面制备微纳孔洞,然后在其一端淀积金属催化颗粒,通入前驱体气氛,使纳米线在沟道中受限进行顺延沟道的平面生长。如此,可以获得位置、直径和形貌都可控的1D纳米线沟道。面向规模化器件应用,其主要技术挑战在于如何高效制备微纳孔洞阵列,由于纳米线的直径直接由孔径大小调控,制备直径在几十到百纳米量级的孔洞往往需要昂贵的高精度电子束EBL刻蚀工艺。使用阳极氧化多孔氧化铝结构可以帮助制备高密度纳米级孔径,但是如何使之在平面上精确定位以及实现对单个纳米线沟道的独立栅极调控还有巨大的技术挑战。

图2:利用衬底表面纳米孔径引导沟道实现的平面硅纳米线生长和原型电学器件。

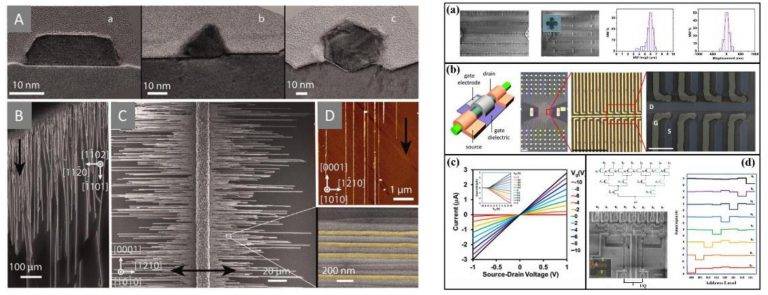

2)其次,基于VLS生长模式,利用晶体衬底本身的晶格外延方向实现同质/异质定向引导。例如在晶态衬底(蓝宝石或者晶硅等)上,由于外延生长界面在降低系统能量上更为有利,故而可以控制自组装平面纳米线在特定方向上定向生长。利用此技术已经实现了各种III-V族、硅锗、金属氧化物以及钙钛矿纳米线的平面引导生长,为规模制备纳米线光电探测、电子逻辑和存储器件提供了关键的生长技术,并已经成功展示了一系列高性能原型功能器件。

图3:(左)在蓝宝石衬底不同晶面上,通过VLS模式实现的GaN纳米线异质外延引导生长。(右)基于异质外延定向生长ZnO纳米线结构制备的电子逻辑器件集成制备。

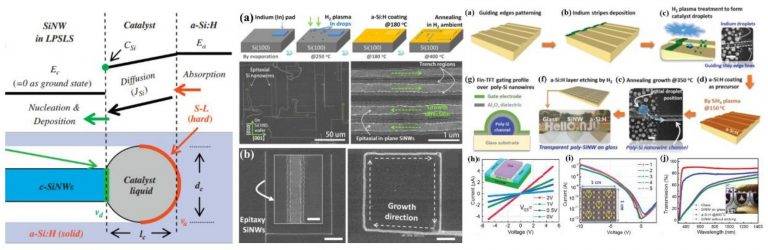

3)基于一种新型的平面固液固(In-Plane-Solid-Liquid-Solid, IPSLS)生长机制,利用非晶薄膜(例如非晶硅,a-Si)作为前驱体,直接将金属催化液滴限制于平面中,生长出自回避、不交叉的平面半导体纳米线。基于此IPSLS生长模式,可以方便地实现平面同质/异质定向外延生长,还能够利用可以方便定义的台阶边缘对纳米线进行精准定位引导。由于不依赖于高精度的电子束刻蚀技术,可以在大面积衬底上规模制备,实现服务于平板显示应用的高性能鳍形纳米线薄膜晶体管器件。

图4:(左)利用非晶薄膜作为前驱体的IPSLS生长模式机理示意图;(中)基于IPSLS生长模式的平面硅纳米线外延引导生长;(右)利用单边台阶引导实现的平面硅纳米线阵列规模生长和集成技术。

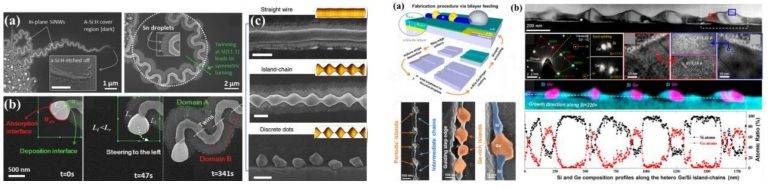

此外,文章还进一步讨论了平面限制纳米线生长为实现纳米线组分和形貌调控带来的新机遇和新技术。介绍了利用平面生长纳米线的“强生长界面相互作用”实现的超朔形能力,以及基于液滴微纳动态调控获得的自发相分离Ge/Si超晶格纳米线结构。

图5:(左)平面纳米线超朔形形貌调控实现的均匀、岛链、弹簧和分立纳米线结构。(右)利用叠层前驱体供给实现的Ge/Si异质岛链超晶格纳米线结构及其组分和结构表征。

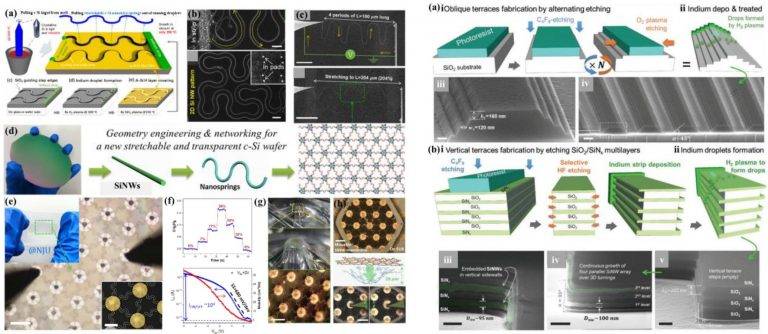

最后,文章还探讨了平面纳米线生长在制备超可拉伸纳米线弹簧沟道和高密度三维集成方向的应用潜力。由于平面纳米线生长线形(line-shape)可以被精确编程调控,可以规模制备超长纳米线2D弹簧结构和阵列,为实现可拉伸电子和光电探测器提供关键的材料和结构基础。此外,文章强调平面纳米线生长调控和集成技术将不仅仅限于衬底水平表面,而实可以被拓展到光刻技术无法直接应用的侧壁表面,从而向z方向延生以获得更高的集成密度和发展空间。

图6:(左)通过平面纳米线线形调控实现的超可拉伸晶硅纳米线沟道,以及连续可拉伸网格结构;(右)利用IPSLS技术在斜坡面或陡直表面上生长的高密度纳米线阵列;

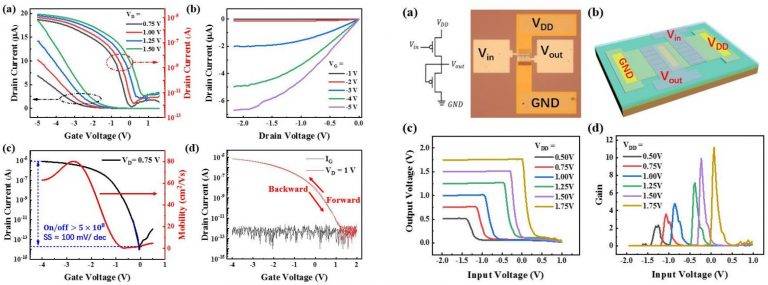

在IPSLS纳米线器件应用方面,课题组在近期成功实现了可定位集成的平面纳米线阵列生长制备技术和高性能场效应薄膜晶体管(TFT)器件,展示了高开关比Ion/Ioff>5x108,低亚阈值摆幅<100 mV/dec和较高的空穴迁移率80 cm2/Vs以及反相器逻辑功能。为开发新一代大面积、高清和柔性LCD和AMOLED平板显示,高灵敏度生物/化学气氛传感和可穿戴电子器件奠定了关键基础。

图7:(左)纳米线鳍形晶体管fin-FET器件特性;(右)以及所实现的反相器逻辑器件。

以上综述内容近期发表于Advanced Materials 31, 1903945 (2019) DOI: 10.1002/adma.201903945, Planar Growth, Integration, and Applications of Semiconducting Nanowires,https://doi.org/10.1002/adma.201903945, 孙莹同学,董泰阁同学为共同第一作者,余林蔚教授和徐骏教授为通信作者。

平面纳米线FET器件研究工作内容,近期发表于IEEE Electron Device Letters, doi: 10.1109/LED.2019.2953116 (2019), High performance Si nanowire TFTs with ultrahigh on/off current ratio and steep subthreshold swing, https://ieeexplore.ieee.org/document/8896986尹涵同学是第一作者,余林蔚教授和潘丹峰工程师为通讯作者。

此工作得到南京大学电子学院陈坤基教授、施毅教授和王军转副教授的大力支持,以及自然科学基金面上项目、重点研发计划和江苏省杰出青年基金等项目的资金支持,在此一并表示衷心的感谢!

(注:以上图片均来自于相关论文,引文参见文中对应引用)

本文由南京大学余林蔚、徐骏教授课题组供稿。